RI5CY 介绍

Introduction of RI5CY(CV32E40P)

什么是 RI5CY

- 4阶段流水线,顺序的 32-bit 的 RISC-V 处理核,后改名为 CV32E40P,但为方便叙述,以下均称之为 RI5CY。

- RI5CY 支持的最基础的 RISC-V 指令集版本(最新)的是 RV32I Base Integer Instruction Set version 2.1。除此之外,它还支持以下 RISC-V 指令集:

- C : Standard Extension for Compressed Instructions 2.0

- M : Standard Extension for Integer Multiplication and Division 2.0

- Zicsr : Control and Status Register Instructions 2.0

- Zifencei : Instruction-Fetch Fence 2.0

- F : Single-Precision Floating-Point 2.2

- 它的 ISA 不仅支持最基本的 RISC-V 指令集,还增添了如下指令:

- 乘加指令 (multiple additional instructions)

- 硬件循环 (hardware loops)

- 后累加装载指令 (post-increment load-store instructions)

- 额外的 ALU 运算指令

- 由 OpenHW Group 开发,这里是它的用户手册,会有更多详细的介绍,以及它的源代码。

OpenHW Group 是什么来头

OpenHw 是一个非盈利的国际组织。该组织的软硬件开发人员在开源核 (open-source core),相关IP (related IP),工具和软件等开发方面进行协作。OpenHW 提供了一个基础架构,用于托管符合行业最佳实践的高质量开源硬件开发。

OpenHW 组织属于 CORE-V Family。CORE-V 是一系列基于RISC-V,以及为电子系统设计师提供相关的处理器子系统 IP,工具和软件的开源核项目。CORE-V Family 在硅片和 FPGA 优化实现中提供符合行业的高质量核心 IP。

OpenHW 组织的主要技术负责人都在国内外非常有名的研究机构或企业任职。该组织的董事会主席 Rob同时还是 RISC-V International 董事会成员。 Rob也是IEEE的高级成员,兼任 Southern Methodist University 和 the University of Texas 的兼职教授。

从 RI5CY 到 CV32E40P

从官方用户手册上可以了解到,CV32E40P 最初是基于 OpenRISC ISA 的 OR10N CPU 核的分支。在去年我开始了解该处理核的这个时候,其正式名字还是 RI5CY,到了今年就更名为 CV32E40P,项目更名一定程度上伴随着组织关系的变化。之前 RI5CY 的项目主要是由 PULP Platform 负责。

PULP Platform 的全称为 Parallel Ultra Low Power Platform。该组织的主要工作是开发开源的、可扩展的软硬件研究开发平台,以突破毫瓦功率级别的能效墙,并满足需要灵活处理数据流的 loT 应用的计算需求,例如加速度计,低分辨率摄像头,麦克风阵列和生命体征监视器。

在 OpenHW Group 成立之初,PULP加入了这个组织,并将一些有关 RISC-V 核的实现工程转移到了 OpenHW Group 组织之下,其中 RI5CY 便是其中之一。

RI5CY 的特点

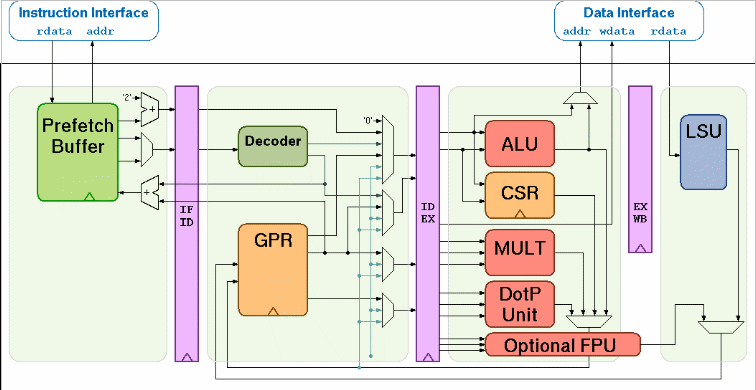

之前提到,RI5CY 是一个顺序的4阶段流水线 32-bit 的 RISC-V 处理核。它的流水线设计图如下:

RI5CY 是一个非常好的自定义处理核的起点,这也是它在科研圈较受欢迎的原因之一。当然这相当程度上归功于 1)开发组人员对它的良好维护,2)非常清晰明确的源代码,3)能被综合或仿真工具实例化,4)有 Verilator 模型的测试平台,5)可在 FPGA 和 ASIC 上高效实例化。

在最初开发 RI5CY 的过程中 PULP Platform 就制定了一个设计目标,追求高能效的信号处理。为此,它们添加了乘加指令 (multiple additional instructions)、硬件循环 (hardware loops)、后累加装载指令 (post-increment load-store instructions)和额外的 ALU 运算指令(min, max, absolute value)。这样一来,可以减少要处理的指令,减少能耗。

除了在 ISA 上做增添外,设计人员加入了中断 (Interrupts)、异常 (Exceptions)、事件 (Events)、调试 (Debug)、性能 (Performance Counters) 等多个功能。